На заре собственного возникновения в 80-х гг. прошлого века предопределяемые матрицы FPGA (ПЛИС) играли в роли связывающего звена между разрывной логикой и, на самом деле, представляли собой эластично предопределяемый внешний вид. По мере улучшения матриц и с повышением насыщенности и числа вентилей в их составе матрицы стали готовы на большее — работать в роли ускорителей вычислений определённых задач. Сегодня сетка FPGA является полновесным сопроцессором, но усилиями компании Intel матрицы могут размещаться на одинаковой подложке с главным микропроцессором. Может ли быть что-нибудь лучше? Логично, лишь сетка, напрямую встроенная в микролит микропроцессора.

Achronix

Матрицы для интеграции в состав монокристаллических моделей (и микропроцессоров) рекомендовала организация Achronix. Эксперты компании спроектировали целиком многофункциональный и готовый к интеграции в посторонние решения блок вделываемой матрицы либо eFPGA. Решение идет на базе покупки лицензии на эту умную собственность Achronix. В компании рассчитывают, что распределение eFPGA существенно повысит сезонную выручку компании, которая в 2014 г пришла к доходности. Так, в 2016 году прибыль Achronix гарантирует добиться $12 млрд, но в 2017 году, благодаря движению eFPGA, пробьёт потолок в $40 млрд ежегодно.

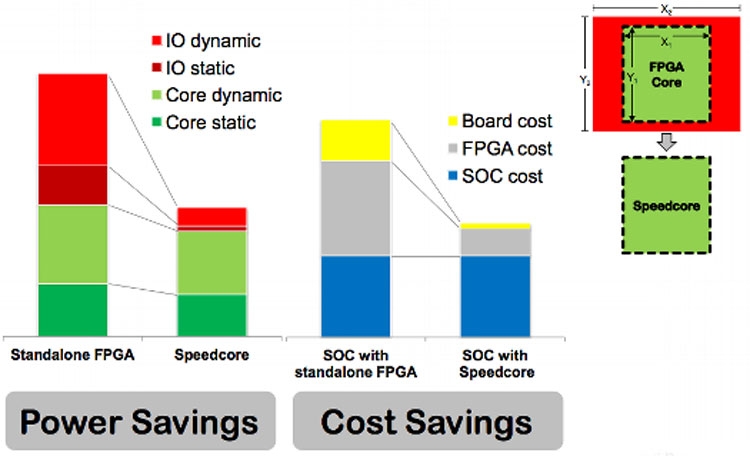

Интеграция матрицы в SoC убирает эффект «бутыльного горлышка» — предельно открывает потенциал по размену данными между матрицей и вычисляемыми ядрами микропроцессора. Задержки при послании к eFPGA уменьшаются до 2 нс, в то время как обычные задержки при послании к в отдельности стоящей сетке одинаковы 30 нс и способны достигать 100 нс. Также понижается площадь кристалла, выделенного под матрицу, и уменьшаются её употребление и себестоимость — всё это, в первую очередь, за счёт освобождения от «ненужных» интерфейсов, которые нужны в отдельности утверждаемым FPGA.

Интеграция — это всегда рентабельно (Achronix)

Нужно обозначить, что представленные организацией Achronix блоки eFPGA Speedcore IP основываются на той же самой архитектуре и применяют те же приборы для работы, что и прошлые «разрывные» матрицы Speedster 22i. Другими словами, покупатели Achronix не будут чувствовать неприятностей, проходя на работу с интегрированными матрицами eFPGA Speedcore. Любопытно другое.

Матрицы Speedster 22i по заявкам Achronix производит организация Intel, для чего применяет 22-нм FinFET процесс. Организация Achronix одна из немногих, кто сообщил предзаказ на производство чипов договорному отряду Custom Foundry компании Intel. Блоки eFPGA Speedcore IP, наоборот, сделаны с прицелом на изготовление компании TSMC с применением техпроцесса 16FF+. Также в компании рассказали, что проводятся подготовки новой версии eFPGA IP для производства с применением 7-нм технических общепризнанных мерок. Вот что обозначает завалить актуальный переход на свежий процесс, от чего пострадала Intel на раунде внедрения 14-нм технических общепризнанных мерок.

Ноябрь 12th, 2022

Ноябрь 12th, 2022  raven000

raven000  Опубликовано в рубрике

Опубликовано в рубрике